# DMA Video Data Transmission over PCI Express Thomas Zerrer

History:

- founded in 2005

- Office in Hildrizhausen, near Stuttgart

- Team of 4 Engineers

- Customers from the Industrial, Test & Measurement and Automotive branches

- Xilinx Alliance Partner / Intel Partner

## **Objectives:**

- Understand the structure and basic terms of a PCI Express System

- Estimate the data throughput at a given Link width / Link speed

- Advantages of DMA Datatransfer over Memory Read Requests

- typical FPGA architectures for transmitting DMA Data

#### Features:

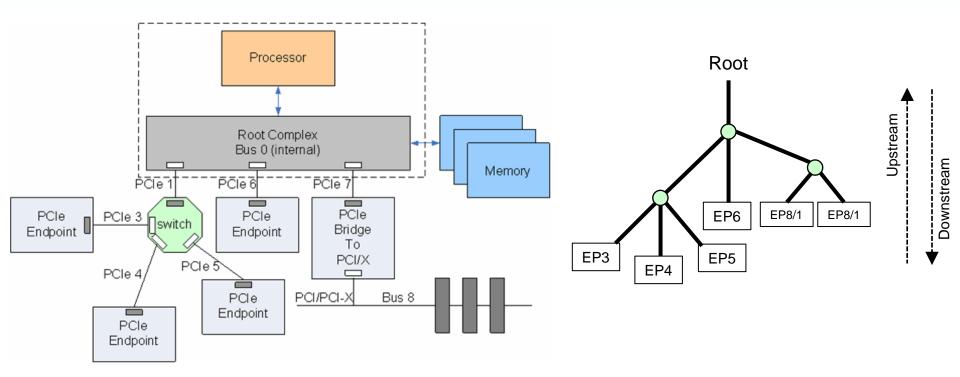

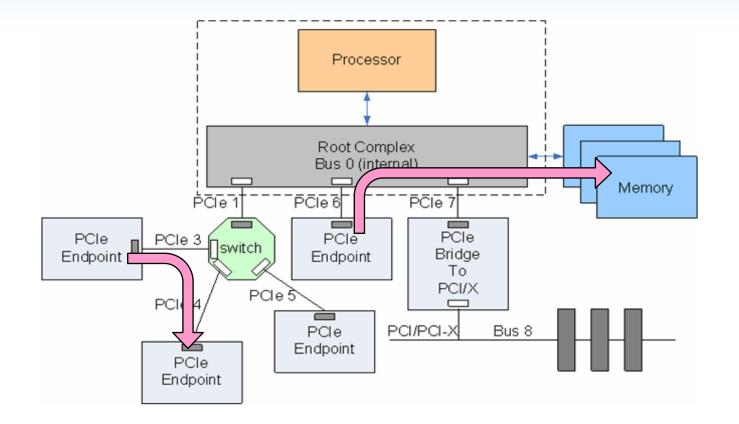

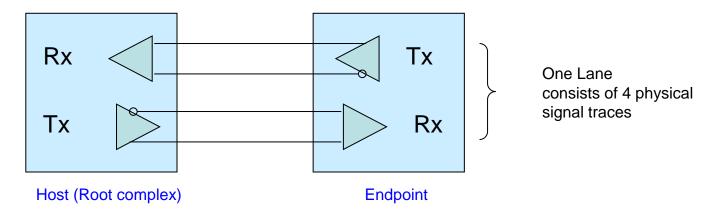

- PCI Express is always a point to point connection

- Switches allow the access of several endpoints from one PCIe connection (PCIe1)

- Every endpoint can exchange data with the Root Complex or other PCIe endpoints

**Bus Mastering Features:**

• Every endpoint can be a Bus Master and write or request data

- No processor involvement for such direct accesses

- Data Transfer can be to the Rootcomplex (e.g. Memory) or to any PCIe endpoint

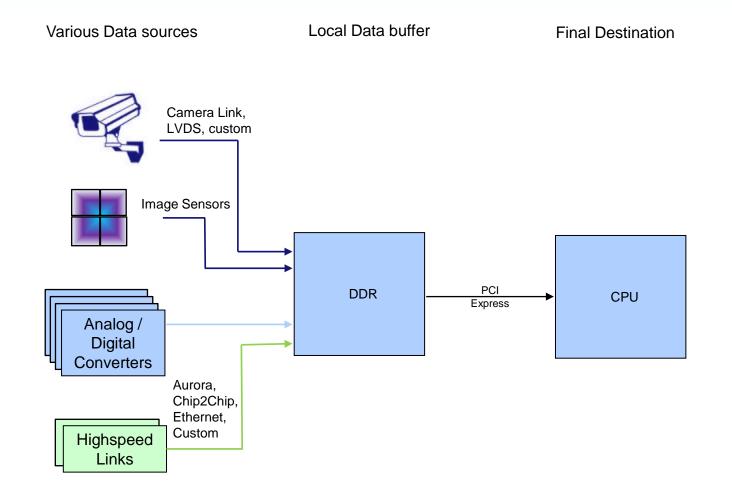

Data Transmission

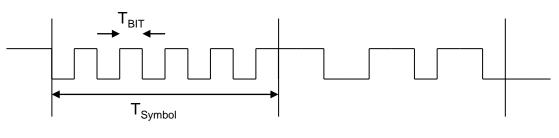

#### PCI-Express is a serial Highspeedlink:

10 Bits = 1 Symbol for Gen 1 & 2, ~8 Bits = 1 Symbol for Gen 3-5

PCI-Express is differential (LVDS) and full duplex:

| T <sub>BIT</sub> : | Re            | elease Date |

|--------------------|---------------|-------------|

| Gen 1 = 400 ps     | 2.5 GBit/s    | 2003        |

| Gen 2 = 200 ps     | 5.0 GBit/s    | 2006        |

| Gen 3 = 125 ps     | 8.0 GBit/s    | 2010        |

| Gen 4 = 62.5 ps    | 16.0 Gbit/s   | 2017        |

| Gen 5 = 31.25 ps   | s 32.0 Gbit/s | 2019        |

The Bitclock is embedded in the data and must be recovered with a Clock Data Recovery circuit

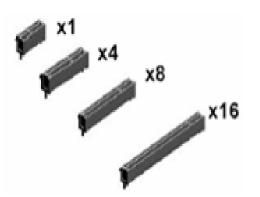

| Link-Width                  |                        | <b>x1</b> | x2    | X4    | <b>x8</b> | x16                                       |

|-----------------------------|------------------------|-----------|-------|-------|-----------|-------------------------------------------|

|                             | Gen 1 : 2.5<br>Gbit/s  | 250       | 500   | 1.000 | 2.000     | x16<br>4.000<br>8.000<br>16.000<br>32.000 |

| Theoretical throughput in   | Gen 2 : 5.0<br>Gbit/s  | 500       | 1.000 | 2.000 | 4.000     | 8.000                                     |

| MByte / s*<br>per direction | Gen 3 : 8.0<br>Gbit/s  | 1.000     | 2.000 | 4.000 | 8.000     | 8.000<br>16.000                           |

|                             | Gen 4 : 16.0<br>Gbit/s | 2.000     | 4.000 | 8.000 | 16.000    | 32.000                                    |

Motherboard Connectors

\* 1 MByte =  $10^6$  Byte

In order to achieve more data throughput than one lane provides, several lanes can be grouped together, forming higher link widths. This is called a multilane link.

Caution: The actual throughput is less than the given values above, because of protocol overhead and other decreasing factors !

### Understanding the maximum payload size (MPS) :

#### Example Data Packets:

| Packet Header | User Data = Payload, 512 Byte |                                |               |               |  |

|---------------|-------------------------------|--------------------------------|---------------|---------------|--|

|               | Packet Header                 | User Data                      | Packet Footer |               |  |

|               |                               |                                |               |               |  |

|               |                               | Packet Header User Data, 128 B |               | Packet Footer |  |

- MPS defines the maximum amount of user data (= payload) contained in a PCI-Express data packet (TLP).

- The higher this value is, the less is the protocol overhead, since Packet header and Packet Footer remain the same.

- The actual MPS value is negotiated during link training between the endpoint and the link partner and remains fixed until powerdown.

- The Spec defines MPS values of 128, 256, 512, 1024, 2048 or 4096 Bytes.

- Important : You have to select the right CPU (Host, Rootport) carefully. MPS > 512 are rare !

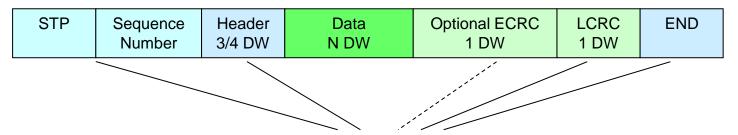

### **TLP Packet:**

Packet Overhead = 5 DW for 32 Bit Addressing and 6 DW for >4 Gbyte Addressing (no ECRC/Digest assumed)

| MPS* in Bytes | 5 DW Overhead  | 5 DW Loss in % | Max Throughput<br>(Gen 1, x1, 5 DW)** | Max Throughput<br>(Gen 1, x1, 6 DW)** |

|---------------|----------------|----------------|---------------------------------------|---------------------------------------|

| 128           | 20 / (128+20)  | 13,5 %         | 216,3                                 | 210,5                                 |

| 256           | 20 / (256+20)  | 7,2 %          | 232                                   | 228,5                                 |

| 512           | 20 / (512+20)  | 3,8 %          | 240,5                                 | 238,75                                |

| 1024          | 20 / (1024+20) | 1,9 %          | 245,3                                 | 244,25                                |

| 4096          | 20 / (4096+20) | 0,5 %          | 248,8                                 | 248,75                                |

\* Maximum Payload Size

\*\* in MByte/s, 1 MB =  $10^6$  Byte

DW = Double Word = 32 Bit

## Bad Signal Integrity causes packet replays

- Every PCIe Data Packet (TLP) contains a CRC checksum (PCIe term "LCRC") in order to ensure the data integrity

- If this TLP is lost or contains a wrong CRC, the sender is informed to resend the TLP

- If the endpoint has to replay the packets very often the effective DMA Performance decreases.

#### Actions:

- The Transceiver Parameter of the endpoint have to optimized according to the effective trace lengths in order to ensure the best quality of the received signal.

- The PCB Layout has to obey high speed rules, typically found at the vendors website

- The host System has to be carefully selected in order to ensure good signal quality

Note : The amount of packet retries can be measured with Smartlogic's DMA Performance Demodesign

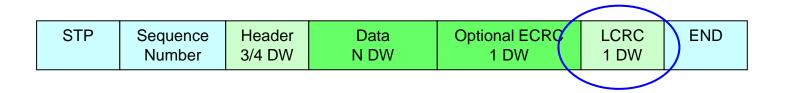

### **Understanding Flow Control**

Each Receiver has a limited RX-Data Buffer:

- Flow Control is used to limit the amount of transmitted data in order to prevent Fifo overflows at the receiver side.

- The Free Space in the RX FIFO is transmitted periodically to the Link Partner in form of a Data Link Layer Packet (DLLP)

## **Flow Control Rules**

- Flow Control is used to limit the amount of transmitted data in order to prevent Fifo overflows at the receiver side.

- Therefore a transmitter is only permitted to send data, if it has enough flow control credits from the link partner.

- If the link partner does not advertise credits, the transmitter is not allowed to send data.

- Since the PCI-Express Protocol defines different categories of incoming data (i.e. completions of read requests, Write requests, etc) different receiver buffers exist, which have their own dedicated credit pools. So it is possible, that an endpoint might be allowed to send completions but is not allowed to send DMA data requests.

- The names of the different credit categories are: posted header, posted data, nonposted header, non-posted data, completion header, completion data.

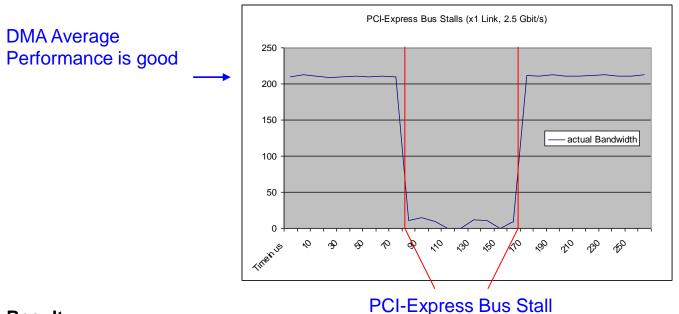

### Slow Flow Control updates from the Host decrease DMA Performance

#### **Result:**

PCIe Bus Stalls are Host dependent. They directly impact the design (i.e. FIFO depths, etc) Good systems show Stall-Times < 10 us. Bad systems show stall-times up to 140 us !

Note : PCIe Bus stall time can be measured with Smartlogic's Performance Demo Design.

|                           | Smartlogi          | ic PCI-Express<br>www.smart |                         | ance Test       | t                  |        |

|---------------------------|--------------------|-----------------------------|-------------------------|-----------------|--------------------|--------|

| Card Information          | <u>1</u>           | Driv                        | ver Informatio          | on              |                    |        |

| FPGA Version:             | 25.01.2017, REV=00 | Drive                       | r Version:              | V1.5.0          |                    |        |

| Link Speed:               | 5.0 GBit           | Physi                       | cal Address DMA Po      | ool: phys=0x8c9 | 3c000 / size=41943 | 04     |

| Link Width:               | X8                 | Numb                        | er of BARs:             | 5               |                    |        |

| Payload Size:             | 256 Byte           | IRQ                         | level:                  | 10              |                    |        |

| Slot Clock:               | 1                  |                             |                         |                 |                    |        |

| 1. Usable Bandwidth       | (WRITE)            |                             | Start Write 3175.798576 | Start Read      | Start Read/Write   | MByte/ |

|                           | (READ)             |                             |                         | 2971.255617     | 2818.393592        | MByte/ |

| 2. Performance Measure    | ment Time          |                             | 27.600                  |                 | 31.100             | s      |

|                           |                    |                             |                         | 29,500          | 31.100             | s      |

| 3. Bytes                  |                    | 87652040704                 |                         |                 |                    |        |

| 4. Maximum PCIe stall tin |                    | 7.872 µ                     | IS                      |                 |                    |        |

| 5. Amount of deadlocks    | > 50.0 µs:         | UN                          |                         |                 |                    |        |

| 6. Max Deadlock:          |                    | 492 (000001ec)              |                         |                 |                    |        |

| 7. Num Deadlock           |                    | 0 (0000000)                 |                         |                 |                    |        |

| 8. PCI-Status             |                    | 424447271 (90822127)        |                         |                 |                    |        |

| 9. PCIe-Retrys during Pe  |                    |                             |                         |                 |                    |        |

| (1 MByte = 1.000.000 B    | ytes)              |                             |                         |                 |                    |        |

|                           |                    |                             |                         |                 |                    |        |

#### Features:

• Performance Measurement for Read & Write Directions to measure Host Parameters like Throughput, MPS, CRC Errors, Stall Time

• Available for Evaluation with Xilinx Demoboards (Bitstream, GUI, Driver) AC701, KC705, KC105, VCU108 and others (see smartlogic Webpage)

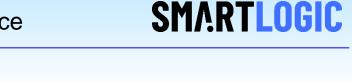

- Read Requests are very inefficient compared with maximum packed MemWrite Requests:

First Reason is the Propagation Delay between Rootport and Endpoint Second Reason is, that the Read Requests never request more than 4-8 DWs

- For Maximum PCIe throughput, Memwrite Requests are necessary

| Link Speed /<br>Width | Туре          | 4 DW Read<br>MBytes / s | 2 DW Read<br>MBytes / s | 1 DW Read<br>MBytes / s |

|-----------------------|---------------|-------------------------|-------------------------|-------------------------|

| G1 / X1               | Typical Slot  | 6,3                     | 3,15                    | 1,6                     |

| G1 / X4               | Typical Slot  | 9,1                     | 4,55                    | 2,3                     |

| G2 / X4               | Typical Slot  | 10,4                    | 5,2                     | 2,6                     |

| G1 / X1               | Graphics Slot | 8,9                     | 4,5                     | 2,25                    |

| G2 / X4               | Graphics Slot | 21,7                    | 10,9                    | 5,5                     |

| G2 / X8               | Graphics Slot | 27,3                    | 13,65                   | 6,9                     |

| G3 / X8               | Graphics Slot | 43,7                    | 21,85                   | 11                      |

$1 \text{ MByte} = 10^6 \text{ Byte}$

Facts:

- PCI Express Read Performance is very poor. Conventional PCI even had a better Read Performance

- The Read Performance depends on the number of switches, the access type and the used OS

The table above provides measured values on a Dell PC System with Win 7-64 Bit. The values may vary on other systems.

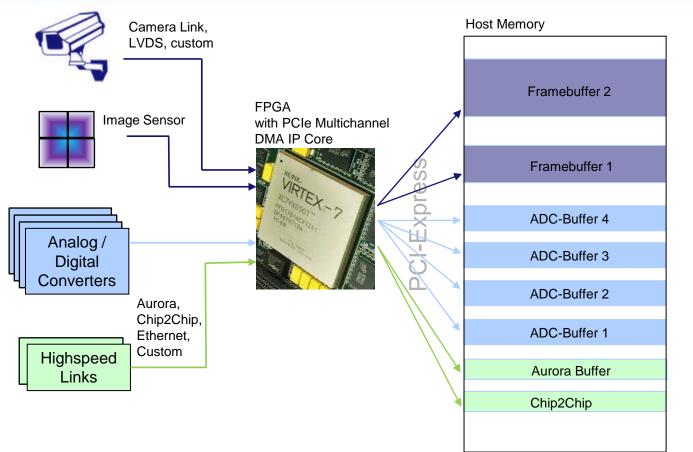

Memory Buffers can be linear or Scatter/Gather Memories

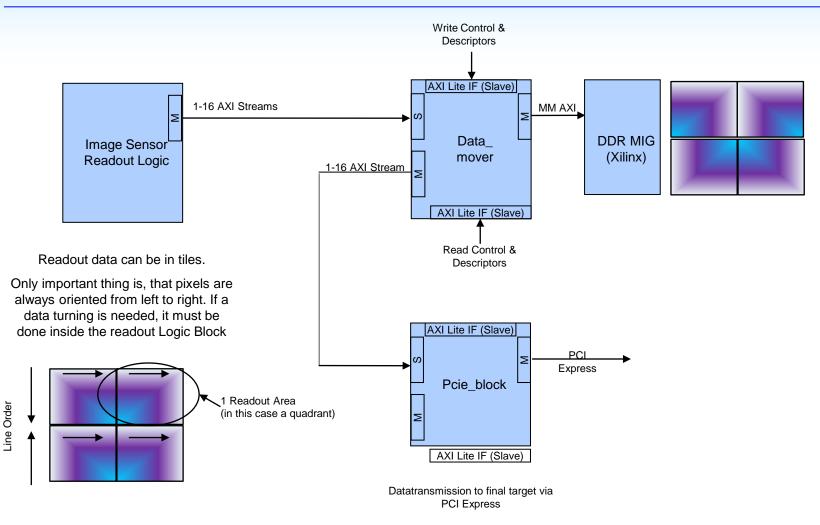

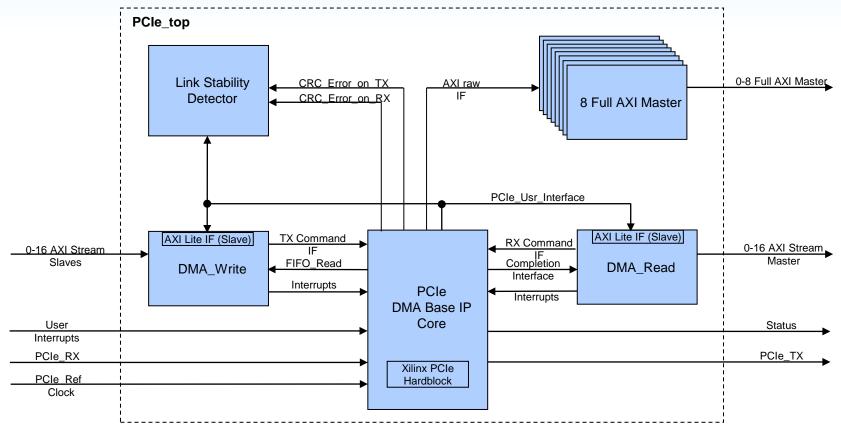

- Up to 16 Datasources possible

- Each Datasource is stored in a separate Memory Buffer

- Core cares for complete addressmanagment, User only supplies data via AXI Stream Interfaces

- The destination can be the Host Memory (as shown) or an other PCIe endpoint Device

- Manage Multiple AXI Streams to AXI Memory mapped (Datamover)

- Provide suitable addressing schemes

- Transmit multiple AXI Streams over PCI Express (PCIe Block)

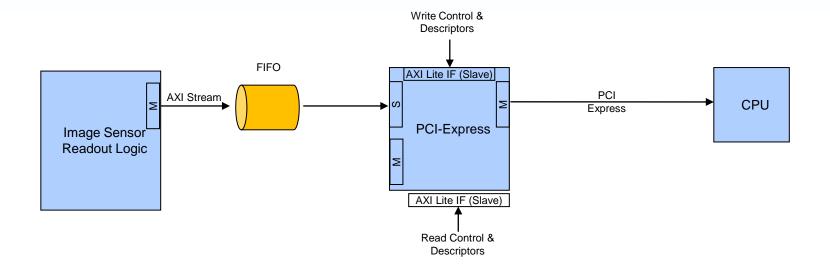

It is possible to transmit the DMA Data without a DDR Framebuffer, but make sure that :

- SRAM based FIFOs <u>must</u> be provided

- PCI Express Stall Times must be deterministic to calculate FIFO depths

- Required throughput should not exceed 80% of net Link Bandwidth

Highlights:

- Each AXI Stream interface is configurable regarding data width and has ist own clock input.

- Unused AXI Master / Slaves do not use Logic resources.

- Link Stability detector for production testing (i.e. soldering problems) for PCB Layout validation

- Full License with Timebomb

## Interesse an vertiefter Schulung?

- Anbindung von GPUs

- DMA Speicher : Scatter / Gather und linear contiguous Speicher (Vor- und Nachteile)

- isochrone Datentransfers

- Advanced PCIe Debugging (IBERT Eyediagrams, Flow Control Problems, Receiver Buffer Overflows, System Freezes und mehr)

| Section PCI-Express Performance Test                                   |                       |                   |           |                  |                  |                   |         |

|------------------------------------------------------------------------|-----------------------|-------------------|-----------|------------------|------------------|-------------------|---------|

| PCI-Express Performance Test SMARTLOGIC<br>smart PCI-Express solutions |                       |                   |           |                  |                  |                   |         |

| Card Information                                                       | 1                     |                   |           | Driver           | Information      |                   |         |

| FPGA Version:                                                          | -<br>01.08.2018, REV= | 00                |           | Driver Ver       | sion:            | V1.5.0            |         |

| Link Speed:                                                            | 8.0 GBit              |                   |           | Physical A       | ddress DMA Pool: | 0x4076c0000 / 256 | 5M      |

| Link Width:                                                            | X8                    |                   |           |                  |                  | 0x3a7dd2000 / 256 | 6M      |

| Payload Size:                                                          | 256 Byte              |                   |           | Number of        | BARs:            | 5                 |         |

| Slot Clock:                                                            | 1                     |                   |           | IRQ level:       |                  | 10                |         |

| Settings:                                                              |                       |                   |           |                  |                  |                   |         |

| OMA Buffer 1 & 2                                                       |                       |                   | Size of S | treaming Buffer  | IP Performance   | (8kByte)          | •       |

| C DMA Buffer 3 & 4                                                     |                       |                   | Stall-Tim | -<br>e Threshold | 20               |                   |         |

|                                                                        |                       |                   | o can min | e milesnola      | 120              |                   |         |

| Results:                                                               |                       |                   |           |                  |                  |                   |         |

|                                                                        |                       |                   |           | Start Write      | Start Read       | Start Read/Write  |         |

| 1. Usable Bandwidth                                                    | (WRITE)               | 1                 |           | 6374.693869      |                  | 6374.693869       | MByte/s |

|                                                                        | (READ)                |                   |           |                  | 6956.511167      | 6742.464670       | MByte/s |

| 2. Performance Measure                                                 | ment Time             |                   |           | 27.500           |                  | 27.500            | s       |

|                                                                        |                       |                   |           |                  | 25.200           | 26.000            | s       |

| 3. Bytes                                                               |                       | 17530408          | 1408      |                  |                  |                   |         |

| 4. Maximum PCIe stall tim                                              | ne duration           | 0                 | .000 μs   |                  |                  |                   |         |

| 5. Amount of deadlocks :                                               | > 20.0 µs:            |                   | 0 N       |                  |                  |                   |         |

| 6. Max Deadlock:                                                       |                       | 0 (00000          | 000)      |                  |                  |                   |         |

| 7. Num Deadlock                                                        |                       | 0 (00000          | 000)      |                  |                  |                   |         |

| 8. PCI-Status                                                          |                       | 2424512544 (90832 | 2020)     |                  |                  |                   |         |

| 9. PCIe-Retrys during Pe                                               | rformance Test:       | 0                 |           |                  |                  |                   |         |

| (1 MByte = 1.000.000 By                                                | /tes)                 |                   |           |                  |                  |                   |         |

| www.smartlo                                                            | gic.de                |                   |           |                  |                  |                   | Close   |

| Performance Test Done                                                  |                       |                   |           |                  |                  |                   |         |

### Features on CD:

• Performance Measurement for Read & Write Directions to measure Host Parameters like Throughput, MPS, CRC Errors, Stall Time

• Available for Evaluation with Xilinx Demoboards (Bitstream, GUI, Driver) AC701, KC705, KC105, VCU108 and others (see smartlogic Webpage)

• Evaluation of Smartlogic IP : Datamover and Multichannel DMA Flex Core