# Multi-Channel Flex DMA IP Core for PCIe

### **Product Overview**

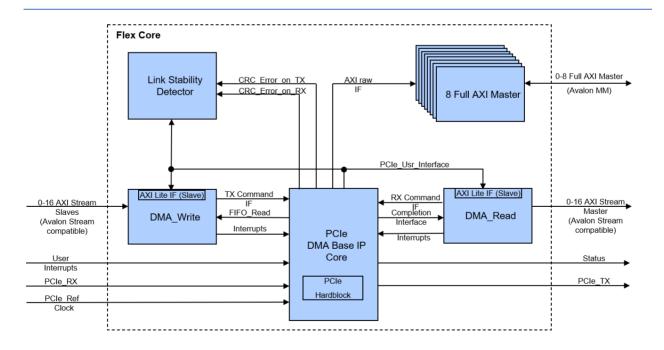

The Multi-Channel DMA IP Core for PCI-Express is a powerful PCIe Endpoint with multiple industry standard AXI Interfaces. Up to 16 independent AXI Stream Slaves write DMA Data to the Host. Up to 16 AXI Stream Masters read DMA Data from the Host and present it to the User Logic. Each channel operates on a separate memory area. Additional 8 AXI4 Masters are available to interface full AXI or AXI-Lite peripherals with the Host.

Due to a powerful arbitration scheme, it is possible to control the priority of each DMA channel over other active channels.

The link stability detector module measures the signal integrity of the PCI Express Link for lab or production tests to prevent shipments of faulty devices.

This IP Core enables the developer to build complex PCI Express endpoints with no specific PCI Express protocol know how. The user only transmits/receives payload data and does not have to build valid PCI Express packets.

#### **IP** Features

- Multi-channel architecture

- Non-blocking approach, an incomplete AXI Stream packet does not block other AXI Streams

- Up to 16 AXI Stream Slave interfaces

- Up to 16 AXI Stream Master interfaces

- Up to 8 AXI Masters to interface user registers

- User transmits / receives only user data without PCIe protocol knowledge

- Supports 32-Bit and 64-Bit addressing

- Independent clocking and data width for each AXI Stream interface

- Adjustable priority control

- Memory size up to 4 GByte per streaming channel

- Based on Xilinx / Intel integrated PCI-Sig compliant PCIe Block (HardIP)

- Link speed Gen 1-3, link widths x1-x8

- Available for all Xilinx and Intel devices

## **Block Diagram**

### Contact

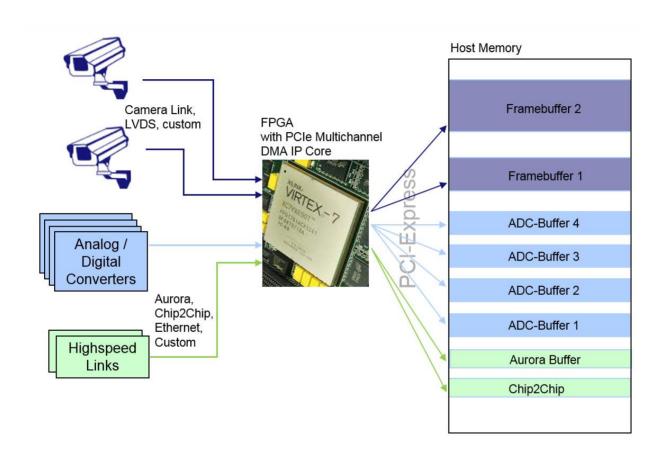

# IP Application Example: "Data Streaming"

Due to its generic architecture, the multi-channel Flex DMA IP Core for PCI Express fits into many applications. The following diagram shows typical streaming applications, where data streams have to be sent ordered to the host memory:

Typical streaming data sources are:

Video cameras, high-speed Analog-Digital-Converter samples, high-speed links like Aurora or others. Up to 64 independent streaming sources with a dedicated target buffer are supported. Each data interface can operate at its own clock domain and its own data width (8, 16, 32, 64, 128 or 256 Bit).

The target can be either the host memory or any other PCI Express endpoint in the system.

#### Contact

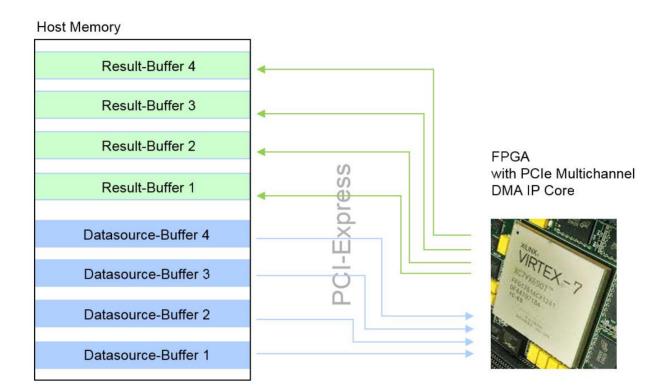

# **IP Application Coprocessor**

Another well-known application is the custom data Coprocessor within a FPGA. The data which has to be processed is either fetched via DMA Read requests from the FPGA or served from the CPU or another PCI Express endpoint. The processed results will be written back into separate memory buffers by using DMA Write requests. Application examples are data encryption and video data processing.

### **FPGA Resource Utilization**

The following table lists different example configurations and the required FPGA resources:

| FPGA Device          | Xilinx Configuration                                                  | LUTs   | LUTR   | FFs    | BRAM |

|----------------------|-----------------------------------------------------------------------|--------|--------|--------|------|

| Artix 7<br>Kintex 7  | 64-bit Architecture, X4, Gen 1<br>4 DMA Write Channels, 1 Master      | 7,221  |        | 6,264  | 20   |

| Artix 7<br>Kintex 7  | 64-bit Architecture, X1, Gen2<br>6 DMA Write Channels, 1 Master       | 8,254  | -      | 6,270  | 26   |

| Artix 7<br>Kintex-7  | 256-bit Architecture, X4, Gen 2<br>4 DMA Write Channels, 1 Master     | 12,286 | 2,837  | 10,075 | 4    |

| Ultrascale           | 256-bit Architecture, X8, Gen3 9 DMA Write and 8 DMA read Channels    | 22,342 | 6,738  | 25,698 | 15   |

|                      | Intel Configuration                                                   | ALMs   |        | FFs    | BRAM |

| Cyclone V<br>Arria V | 256-bit Architecture, X4, Gen2<br>9 DMA Write and 8 DMA Read Channels | 17,462 | 29,319 | 201    |      |

These numbers include the resources of the PCIe Hard-IP and the resources for the AXI Stream FIFOs for each configured channel.

LUTR are distributed RAM cells. The user can choose between BlockRAM or LUT RAM implementation style.

### **Deliverables**

- Encrypted VHDL or source code for easy design flow integration

- Comprehensive user guide and application notes

- Reference design

- Windows / Linux driver package (option)

- PCIe test bench with high-speed simulation mode

- Technical support

### **Evaluation**

This IP Core can be evaluated as an encrypted version. Request a free 30-day evaluation license for ISIM, Modelsim or Aldec simulators at:

### ip@smartlogic.de

Smartlogic is a member of the Intel Partner Alliance and Xilinx's Alliance Program.

#### Contact

Smartlogic GmbH D-71157 Hildrizhausen Phone: (+49) 7031 - 439016 Fax: (+49) 7031 - 439018 www.smartlogic.de

ip@smartlogic.de