AXI Bridge mit DMA für PCIe IP Core

Der AXI Bridge mit DMA IP Core ist Smartlogics ultimative PCIe DMA IP Lösung mit einer leistungsstarken Mischung aus mehreren AXI-Schnittstellen nach Industriestandard. AXI Stream Schnittstellen ermöglichen kontinuierliches Datenstreaming von FPGA zu Host oder von Host zu FPGA. S-AXI Memory Mapped Schnittstellen ermöglichen einfachen Datenzugriff auf entfernte Speicher, um shared Memory oder Peer-to-Peer Anwendungen zu realisieren. Alle Schnittstellen unterstützen den vollständig parallelen Betrieb ohne jegliche Interferenzen. Nicht benötigte Schnittstellen können einzeln abgeschaltet werden und belegen keine logischen Ressourcen. Dieser IP Core ermöglicht dem Entwickler die Entwicklung von komplexen PCI-Express-Endpunkten ohne spezifisches PCI-Express Protokoll Know how. Der Anwender sendet oder empfängt nur Nutzdaten und muss keine gültigen PCI-Express Pakete zusammenstellen. Ein leistungsstarker Kernel Mode Gerätetreiber wird mit dem IP Core für Windows- und Linux Betriebssysteme geliefert, um eine einfache Software Integration des IP Cores zu gewährleisten.

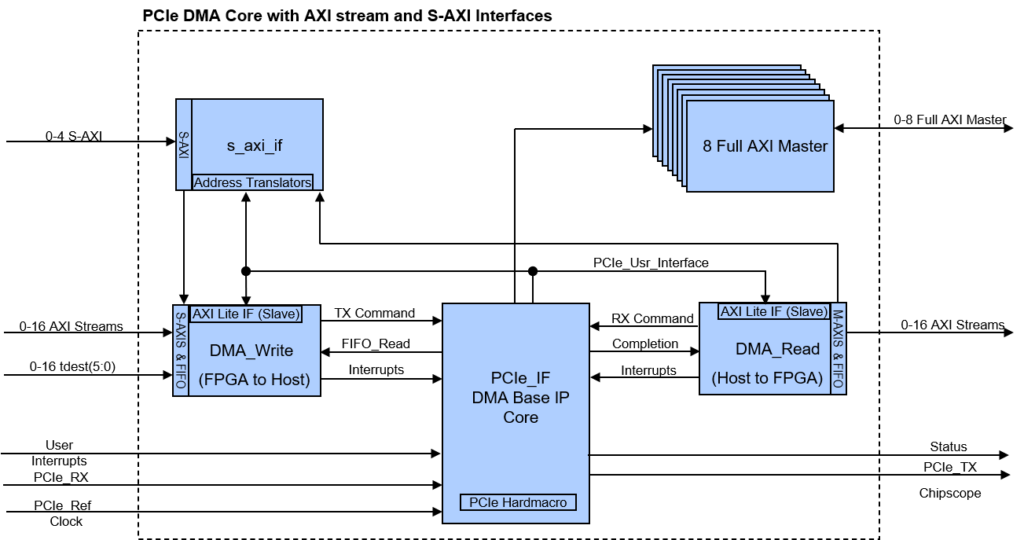

Blockschaltbild

Klicken Sie auf das Blockschaltbild, um es zu vergrößern.

Featureübersicht im Vergleich zum HCC IP Core

AXI Bridge mit DMA für PCIe IP CoreJetzt anfragen | High Channel Count DMA IP CoreJetzt anfragen | |

|---|---|---|

| Number of s-axi interfaces | 0-4 | -- |

| s-axi bit width supported | 32, 64, 128, 256 | -- |

| Separate asynchronous clocks for s-axi | -- | |

| s-axi WSTRB supported | -- | |

| Upstream : Number of s-axis interfaces | 16 | 16 |

| Number of supported DMA channels | 64 | 64 |

| Upstream : continuous streaming of fixed and variable sized packets | ||

| Upstream : s_axis_tdest port to access several buffers | ||

| Upstream : Avalon stream flavor of tready | ||

| Max link width for Gen 1 & 2 | X16 | X16 |

| Max link width for Gen 3 | X8 | X8 |

| Max link width for Gen 4 | X4 | X4 |

| AXI Stream bit width support (s-axis/m-axis) | 8, 16, 32, 64, 128, 256 | 8, 16, 32, 64, 128, 256 |

| MSI-X support | ||

| Downstream : Number of m-axis interfaces | 16 | 16 |

| Downstream : fixed and variable sized transfers | ||

| Downstream : Byte resolution with tkeep | ||

| Superior downstream performance | ||

| Ethernet application support | ||

| GStreamer compatible | ||

| Multi-function support (for selected devices) | Option | Option |

Anwendung AXI Bridge mit DMA für PCIe IP Core

Eine von vielen typischen Anwendungen des AXI Bridge mit DMA für PCIe IP Cores sind Ethernet Anwendungen.

Mehr erfahren