High Channel Count DMA IP Core für PCI Express

Der High Channel Count DMA IP Core für PCI Express wurde speziell für Anwendungen mit sehr vielen Datenquellen für höchsten Durchsatz entwickelt. Bis zu 64 Datenströme können verwaltet werden und im Host Memory mittels DMA in separaten Speicherbereichen abgelegt werden. Für das Interfacing mit User Logik stehen bis zu 8 AXI4 Master (Full/Lite) zur Verfügung. Darüber hinaus wird das Lesen von Daten per DMA mit bis zu 16 AXI Stream Mastern unterstützt.

Dieser IP Core ermöglicht es, einen komplexen PCIe Endpoint ohne spezifisches PCI Express Know How aufzubauen. Der Anwender übergibt bzw. empfängt nur Nutzdaten und muss sich nicht um die Erzeugung von PCI Express Paketen kümmern. Sowohl Datenstreaming, Ethernet Anwendungen als auch Coprozessor Anwendungen können damit in kürzester Zeit realisiert werden.

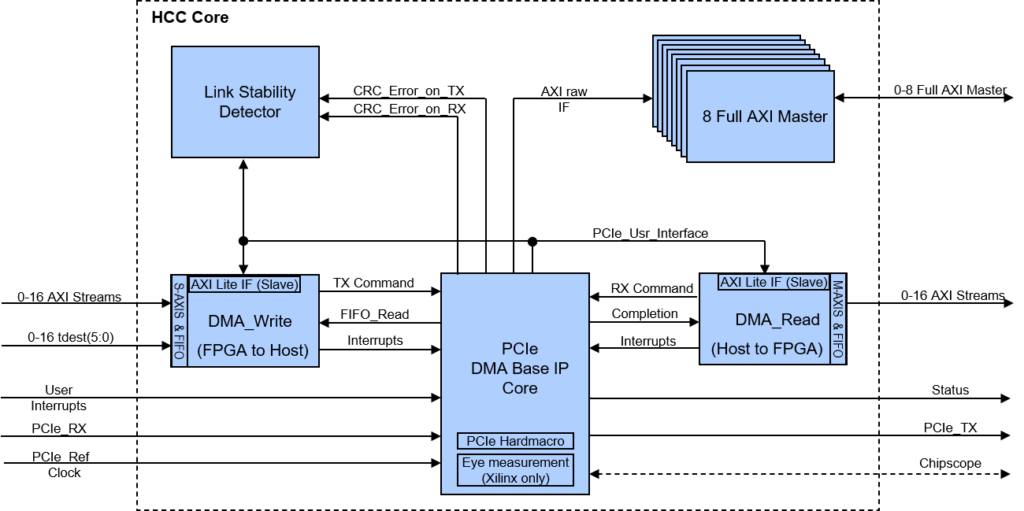

Blockschaltbild

Das nebenstehende Blockschaltbild zeigt den Aufbau des DMA HCC IP Cores. Das DMA Write Modul erlaubt es bis zu 16 AXI Stream Slaves für die DMA Datenübertragung zum Host aufzumachen. Dabei überträgt jedes AXI stream interface die Daten in einen eigenen DMA Speicher. Die umgekehrte Transferrichtung wird mittels des DMA Read Moduls realisiert, das selbsttätig Daten aus dem Hostspeicher anfordert und auf AXI Stream Mastern ausgibt. Für die Anbindung von User Registern können bis zu 8 Memory Mapped AXI Master benutzt werden.

Klicken Sie auf das Blockschaltbild, um es zu vergrößern.

Featureübersicht im Vergleich zum Flex IP Core

High Channel Count DMA IP CoreJetzt anfragen | Multi-Channel Flex DMA IP CoreJetzt anfragen | |

|---|---|---|

| Number of s-axi interfaces | -- | -- |

| s-axi bit width supported | -- | -- |

| Separate asynchronous clocks for s-axi | -- | -- |

| s-axi WSTRB supported | -- | -- |

| Upstream : Number of s_axis interfaces | 16 | 16 |

| Number of supported DMA channels | 64 | 16 |

| Upstream : continuous streaming of fixed and variable sized packets | ||

| Upstream : s_axis_tdest port to access several buffers | -- | |

| Upstream : Avalon stream flavor of tready | -- | |

| Max link width for Gen 1 & 2 | X16 | X8 |

| Max link width for Gen 3 | X8 | X8 |

| Max link width for Gen 4 | X4 | -- |

| AXI Stream bit width support (s-axis/m-axis) | 8, 16, 32, 64, 128, 256 | 8, 16, 32, 64, 128, 256 |

| MSI-X support | -- | |

| Downstream : Number of m-axis interfaces | 16 | 16 |

| Downstream : fixed and variable sized transfers | Fixed size only | |

| Downstream : Byte resolution with tkeep | -- | |

| Superior downstream performance | -- | |

| Ethernet application support | -- | |

| GStreamer compatible | ||

| Multi-function support (for selected devices) | Option | Option |

Anwendung DMA HCC IP Core

Eine von vielen typischen Anwendungen des DMA HCC IP Cores sind Ethernet Anwendungen.

Mehr erfahren