Multi-Channel AXI DMA Engine

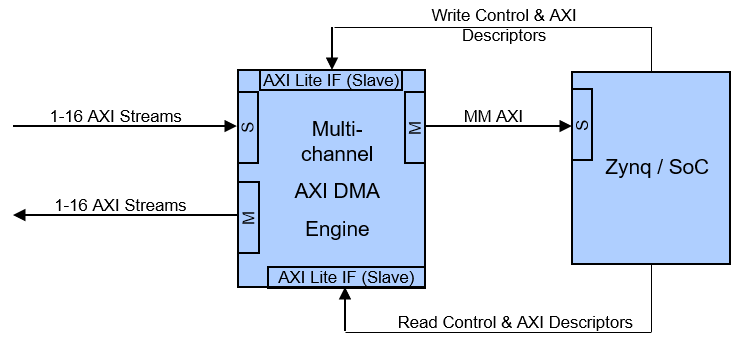

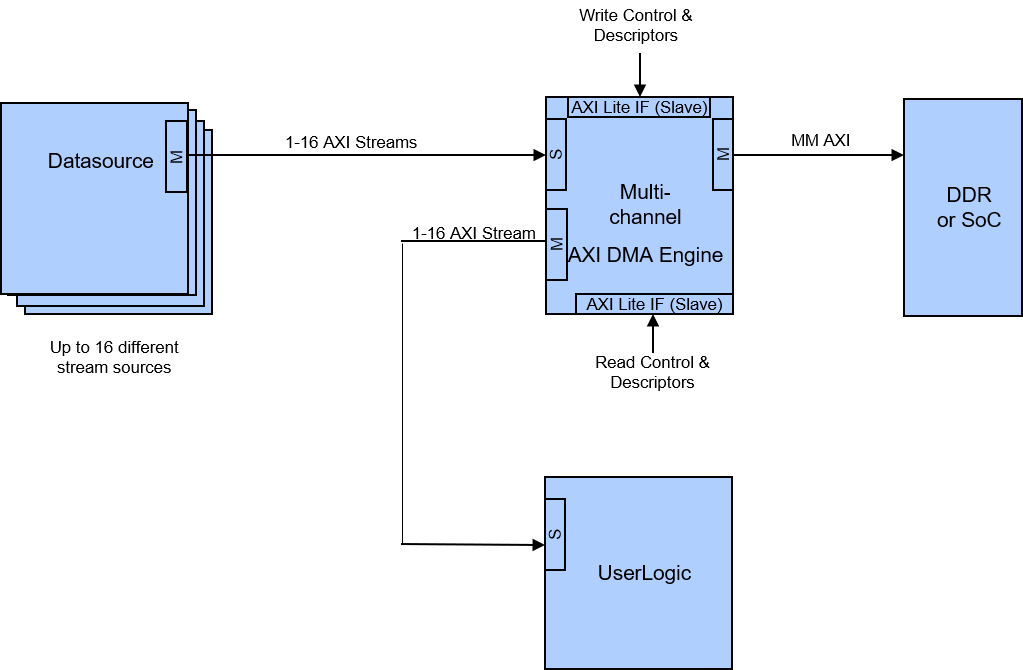

Der multi-channel AXI DMA Engine IP Core verbindet die AXI Stream und die AXI Memory mapped Welt über eine leistungsfähige DMA Engine. Daten von bis zu 16 AXI Stream Slave Eingängen können parallel in AXI memory mapped (z.B. DDR Speicher) geschrieben und wieder ausgelesen werden. Mit den AXI Stream Mastern können Daten aktiv ausgelesen werden und dann in mehreren Streams von nachfolgenden DSP Einheiten verarbeitet werden. Flexible programmierbare Adressgeneratoren erlauben es dabei, die Daten nicht nur linear aufsteigend, sondern auch abwärts oder in Abschnitten sogenannte Regions of Interests (ROI) zu schreiben. Damit wird es möglich, bereits mit dem IP Core eine Sortierung der Reihenfolge der Daten zu realisieren, um nachfolgenden algorithmischen Einheiten die Weiterverarbeitung erheblich zu erleichtern.

Typische Anwendungen

Die multi-channel AXI DMA Engine kommt bei SoC basierten FPGAs oft zum Einsatz, bei denen AXI Stream / Avalon Stream basierte Datenströme wie Kameradaten oder A/D Wandler Daten ins DDR des SoC gestreamed werden müssen. Der mitgelieferte Linuxtreiber erlaubt mit seiner high-level User mode Library den schnellen und sehr einfachen Zugriff auf die Daten. Durch die Kompatibilität des Treibers mit GStreamer steht dem Anwender dadurch ein sehr leistungsfähiges Open-source Videoframework zur Weiterverarbeitung zur Verfügung.

Dieser IP Core kommt aber auch in nicht SoC basierten FPGAs zum Einsatz, wenn zum Beispiel DDR Speicher als Datenpuffer benötigt werden.