Multi-Channel AXI DMA Engine

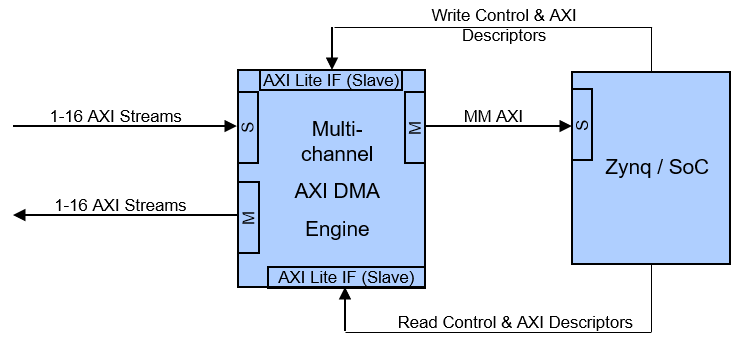

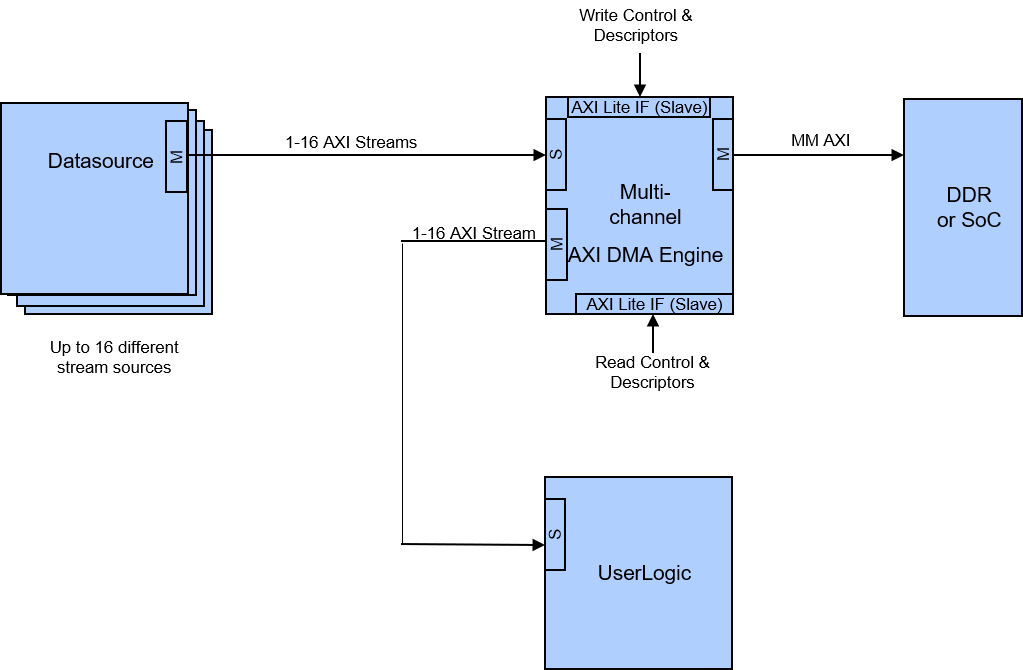

The Multi-Channel AXI DMA Engine IP Core connects the AXI Stream and the AXI memory mapped world via a powerful DMA engine. Data from up to 16 AXI Stream slave inputs can be written to and read from AXI memory mapped (e.g. DDR memory) in parallel. AXI Stream Masters allow data to be actively read and then processed in multiple streams by subsequent DSP units. Flexible programmable address generators allow data to be written not only in linear ascending order, but also in descending order or in sections, so-called Regions of Interests (ROI). This makes it possible to sort the sequence of the data already with the IP core in order to make further processing considerably easier for subsequent algorithmic units.

Typical applications

The Multi-Channel AXI DMA Engine is often used with SoC based FPGAs where AXI Stream / Avalon Stream based data streams like camera data or A/D converter data have to be streamed into the DDR of the SoC. The included Linux driver with its high-level user mode library allows fast and very easy access to the data. The compatibility of the driver with GStreamer provides the user with a very powerful open-source video framework for further processing.

This IP core is also used in non-SoC based FPGAs, for example when DDR memory is required as a data buffer.

Click to enlarge