AXI Bridge with DMA for PCIe IP Core

The AXI Bridge with DMA IP core is Smartlogic’s ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces. AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or peer-to-peer applications.

All interfaces support fully parallel operation without any interferences. Interfaces that are not required can be turned off individually and do not occupy logic resources.

This IP core enables the developer to build complex PCI Express endpoints with no specific PCI Express protocol know-how. The user only transmits or receives payload data and does not have to assemble valid PCI Express packets. A powerful kernel mode device driver is shipped with the IP for Windows and Linux OS to ensure easy software integration of the core.

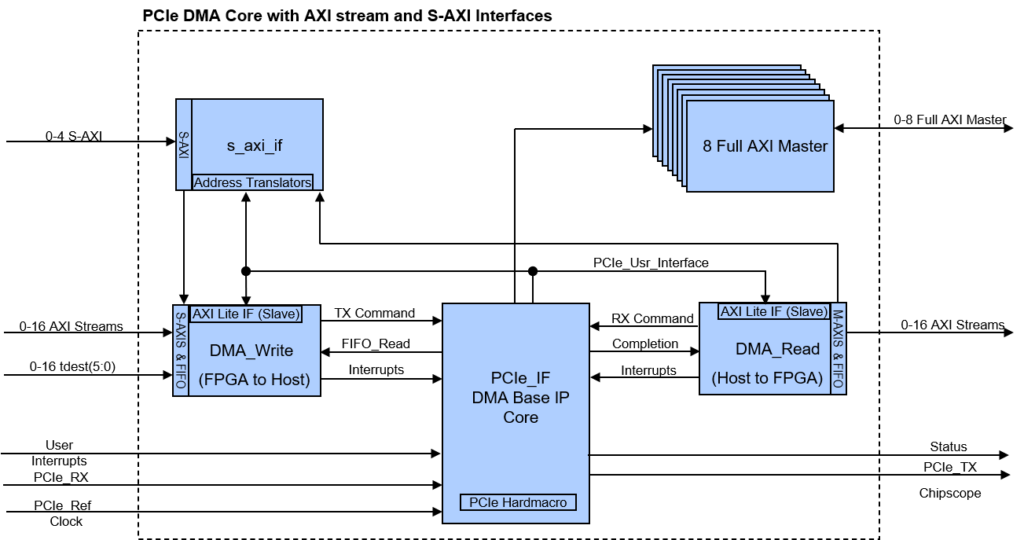

Block diagram

The AXI Bridge with DMA IP core is Smartlogic’s ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces. AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.

All interfaces support fully parallel operation without any interferences. Interfaces that are not required can be turned off individually and do not occupy logic resources.

This IP core enables the developer to build complex PCI Express endpoints with no specific PCI Express protocol know-how. The user only transmits or receives payload data and does not have to assemble valid PCI Express packets.

A powerful kernel mode device driver is shipped with the IP for Windows and Linux OS to ensure easy software integration of the core.

Click on the block diagram to enlarge it.

Feature overview compared to High Channel Count DMA IP Core

AXI Bridge with DMA for PCIe IP CoreInquiry | High Channel Count DMA IP CoreInquiry | |

|---|---|---|

| Number of s-axi interfaces | 0 - 4 | -- |

| s-axi bit width supported | 32, 64, 128, 256 | -- |

| Separate asynchronous clocks for s-axi | -- | |

| s-axi WSTRB supported | -- | |

| Upstream : Number of s-axis interfaces | 16 | 16 |

| Number of supported DMA channels | 64 | 64 |

| Upstream : continuous streaming of fixed and variable sized packets | ||

| Upstream : s_axis_tdest port to access several buffers | ||

| Upstream : Avalon stream flavor of tready | ||

| Max link width for Gen 1 & 2 | X16 | X16 |

| Max link width for Gen 3 | X8 | X8 |

| Max link width for Gen 4 | X4 | X4 |

| AXI Stream bit width support (s-axis/m-axis) | 8, 16, 32, 64, 128, 256 | 8, 16, 32, 64, 128, 256 |

| MSI-X support | ||

| Downstream : Number of m-axis interfaces | 16 | 16 |

| Downstream : fixed and variable sized transfers | ||

| Downstream : Byte resolution with tkeep | ||

| Superior downstream performance | ||

| Ethernet application support | ||

| GStreamer compatible | ||

| Multi-function support (for selected devices) | Option | Option |

Application AXI Bridge with DMA for PCIe IP Core

One of many typical applications of the AXI Bridge with DMA for PCIe IP Core are Ethernet applications.

Learn more