Multi-Channel Flex DMA IP Core for PCI Express

The outstanding feature of our PCI-Express Multi-Channel DMA IP core is the special design for the transfer of up to 16 streaming channels into separate target memories of the host system. The channels work completely parallel and cannot block each other. The effective data rate can also be freely selected by means of a separately selectable clock for each channel, in order to keep interfacing as simple as possible.

By integrating parameterizable input FIFOs into the core, the user can also implement a priority scheme if required. This ensures that highly important data channels are not obstructed by lower- level channels.

In addition to the field of streaming applications, the IP Core also targets co-processor applications. The integrated DMA Read module allows data to be read via DMA from any data source, processed and stored at a new destination.

In addition, the IP core offers monitoring of CRC errors on the PCI Express link to quantitatively assess the current signal integrity on an ongoing basis. This means, for example, that modules with poor signal integrity, e.g. caused by soldering problems, can already be detected and sorted out during production testing. Safety-critical applications can be realized much more easily with this feature.

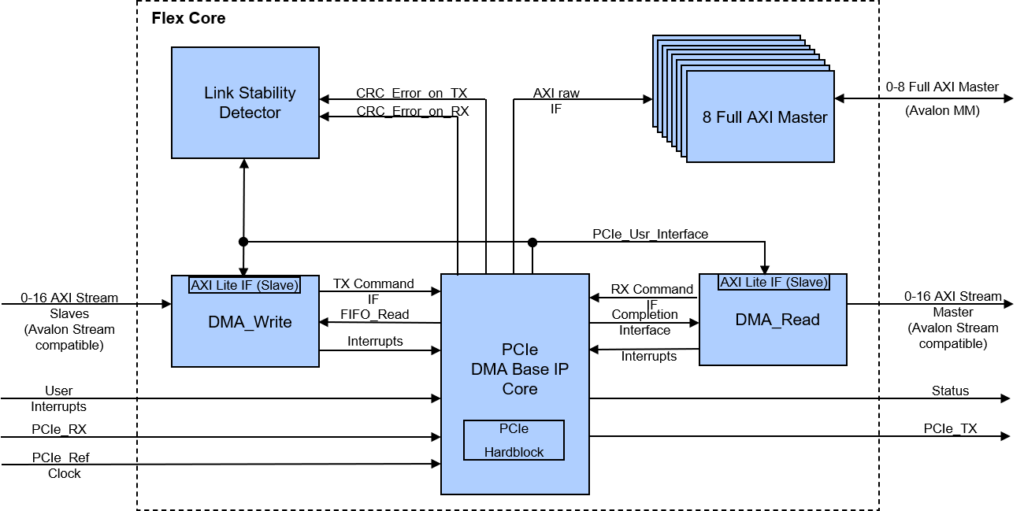

Block diagram

The adjacent block diagram shows the structure of the multi-channel DMA IP core. The DMA Write module allows up to 16 AXI stream slaves to be opened for DMA data transfer to the host. Each AXI stream interface transfers the data into its own DMA memory. The reverse transfer direction is realized by means of the DMA Read module, which automatically requests data from the host memory and outputs it to AXI stream masters. Up to 8 memory mapped AXI masters can be used for the connection of user registers.

Click on the block diagram to enlarge it.

Feature overview compared to High Channel Count DMA IP

Multi-Channel Flex DMA IP CoreInquiry | High Channel Count DMA IP CoreInquiry | |

|---|---|---|

| Number of s-axi interfaces | -- | -- |

| s-axi bit width supported | -- | -- |

| Separate asynchronous clocks for s-axi | -- | -- |

| s-axi WSTRB supported | -- | -- |

| Upstream : Number of s_axis interfaces | 16 | 16 |

| Number of supported DMA channels | 16 | 64 |

| Number of supported DMA channels | ||

| Upstream : s_axis_tdest port to access several buffers | -- | |

| Upstream : Avalon stream flavor of tready | -- | |

| Max link width for Gen 1 & 2 | X8 | X16 |

| Max link width for Gen3 | X8 | X8 |

| Max link width for Gen 4 | -- | X4 |

| AXI Stream bit width support | 8, 16, 32, 64, 128, 256 | 8, 16, 32, 64, 128, 256 |

| MSI-X support | -- | |

| Downstream : Number of m-axis interfaces | 16 | 16 |

| Downstream : fixed and variable sized transfers | Fixed size only | |

| Downstream : Byte resolution with tkeep | -- | |

| Superior downstream performance | -- | |

| Ethernet application support | -- | |

| GStreamer compatible | ||

| Multi-function support (for selected devices) | Option | Option |

Application Multi-Channel Flex DMA IP Core:

One of many typical applications of the Multi-Channel Flex DMA IP Core are camera applications.

Learn more