High Channel Count DMA IP Core for PCI Express

The High Channel Count DMA IP Core for PCI Express was especially developed for applications with very many data sources for highest throughput. Up to 64 data streams can be managed and stored in separate memory areas in the host memory using DMA. Up to 8 AXI4 masters (full/lite) are available for interfacing with user logic. In addition, reading data via DMA is supported with up to 16 AXI Stream Masters.

This IP core makes it possible to build a complex PCIe endpoint without specific PCI Express know- how. The user only passes or receives user data and does not have to care about the generation of PCI Express packets. Data streaming, Ethernet applications as well as coprocessor applications can be realized in a very short time.

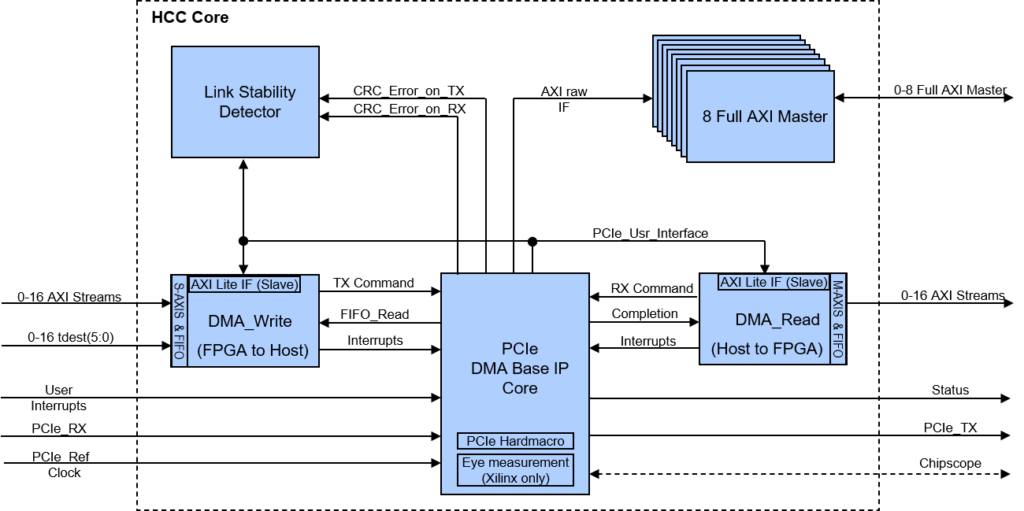

Block diagram

The adjacent block diagram shows the structure of the High Channel Count DMA IP core. The DMA Write module allows up to 16 AXI stream slaves to be opened for DMA data transfer to the host. Each AXI stream interface transfers the data into its own DMA memory. The reverse transfer direction is realized by means of the DMA Read module, which automatically requests data from the host memory and outputs it to AXI stream masters. Up to 8 memory mapped AXI masters can be used for the connection of user registers.

Click on the block diagram to enlarge it.

Feature overview compared to the Multi-Channel Flex DMA IP Core

High Channel Count DMA IP CoreInquiry | Multi-Channel Flex DMA IP CoreInquiry | |

|---|---|---|

| Number of s-axi interfaces | -- | -- |

| s-axi bit width supported | -- | -- |

| Separate asynchronous clocks for s-axi | -- | -- |

| s-axi WSTRB supported | -- | -- |

| Upstream : Number of s_axis interfaces | 16 | 16 |

| Number of supported DMA channels | 64 | 16 |

| Upstream : continuous streaming of fixed and variable sized packets | ||

| Upstream : s_axis_tdest port to access several buffers | -- | |

| Upstream : Avalon stream flavor of tready | -- | |

| Max link width for Gen 1 & 2 | X16 | X8 |

| Max link width for Gen 3 | X8 | X8 |

| Max link width for Gen 4 | X4 | -- |

| AXI Stream bit width support (s-axis/m-axis) | 8, 16, 32, 64, 128, 256 | 8, 16, 32, 64, 128, 256 |

| MSI-X support | -- | |

| Downstream : Number of m-axis interfaces | 16 | 16 |

| Downstream : fixed and variable sized transfers | Fixed size only | |

| Downstream : Byte resolution with tkeep | -- | |

| Superior downstream performance | -- | |

| Ethernet application support | -- | |

| GStreamer compatible | ||

| Multi-function support (for selected devices) | Option | Option |

Application High Channel Count DMA IP:

One of many typical applications of the High Channel Count DMA IP are Ethernet applications.

Learn more